KAmodDIGA: Difference between revisions

From Kamamilabs.com - Wiki

| (One intermediate revision by one other user not shown) | |||

| Line 1: | Line 1: | ||

__jzpdf__ | __jzpdf__ | ||

====== Description ====== | ====== Description ====== | ||

KAmodDIGA is a C/A audio converter made on TS4657 chip from ST. Module make possible to play sounds in digital systems via I2S interface. | [https://kamami.pl/en/kamod-kamami-peripheral-modules/179456-kamoddiga-module-of-a-stereo-24-bit-audio-converter-with-i2s-interface-ts4657-5906623432363.html KAmodDIGA] is a C/A audio converter made on TS4657 chip from ST. Module make possible to play sounds in digital systems via I2S interface. | ||

<center> | <center> | ||

[[File:kamod_diga.jpg|none|400px|thumb|center]] | [[File:kamod_diga.jpg|none|400px|thumb|center]] | ||

Latest revision as of 16:26, 1 November 2024

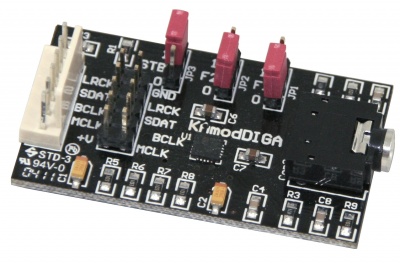

Description

KAmodDIGA is a C/A audio converter made on TS4657 chip from ST. Module make possible to play sounds in digital systems via I2S interface.

Basic parameters

- Stereo C/A TS4657 converter from STMicroelectronics

- I2S interface

- Sampling frequency from 32kHz to 48kHz

- Resolution 16...24 bits

- I2S frame format configurable with jumpers

- Integrated low-pass filters

- Jack stereo connector 3.5mm

- Power supply voltage 3..5.5V

- Standby mode

- I2S connector compatible with Kamami standard

Standard equipment

| Code | Description |

|---|---|

| KAmodDIGA |

|

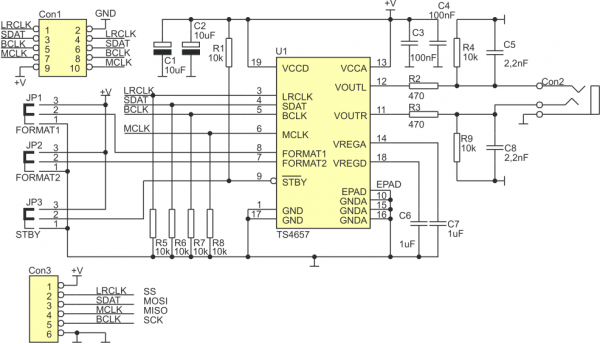

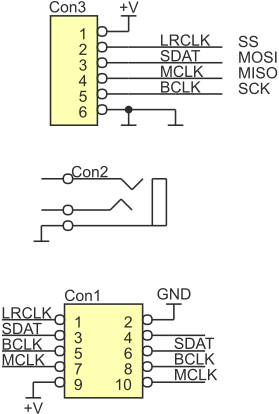

Schematic

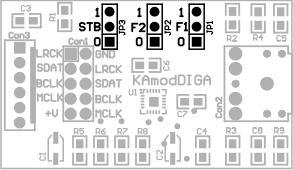

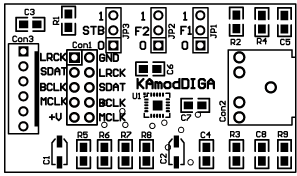

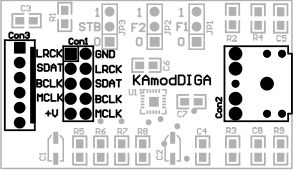

View of board

Connectors

Module is equipped with Con1 and Con3 connectors. They make possible to connect module to the digital system with I2S interface. Con2 connector (Jack stereo 3.5mm) is used to connect a headphones, loudspeaker or audio amplifier (output voltage 2.2V RMS@10 kΩ).

Configuration

STB jumper is used to switch a converter into Standby mode. F1 i F2 jumpers are used for selection of data format, which are converted by converter.

| STB jumper position | Standby mode… |

|---|---|

| 0 | …off |

| 1 | …off |

| F1 jumper | F2 jumper | Data format |

|---|---|---|

| 0 | 0 | 16 bits/channel, processed 16 last transmitted bits (right justified), synchronization with rising edge of BCLK |

| 1 | 0 | 24 bits/channel, processed 24 last transmitted bits, read on rising edge of BCLK |

| 0 | 1 | 16..24 bits/channel, processed the latest transmitted bits (left justified), read on rising edge of BCLK |

| 1 | 1 | I2S, 16..24 bits/channel, read on rising edge of BCLK |