ZL14PLD (PL): Difference between revisions

From Kamamilabs.com - Wiki

No edit summary |

No edit summary Tag: Manual revert |

||

| (9 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

__jzpdf__ | |||

===== Opis ===== | ===== Opis ===== | ||

Moduły dipPLD opracowano z myślą o ułatwieniu powszechnego stosowania układów | Moduły dipPLD opracowano z myślą o ułatwieniu powszechnego stosowania układów CPLD przez konstruktorów, którzy nie mogą lub nie chcą inwestować w zautomatyzowany montaż elementów o relatywnie „gęstym” rastrze rozmieszczenia wyprowadzeń (0,5 mm). | ||

<center> | <center> | ||

[[File:Zl14pld_skos_czarny.jpg|none|400px|thumb|center]] | [[File:Zl14pld_skos_czarny.jpg|none|400px|thumb|center]] | ||

</center> | </center> | ||

===== Podstawowe parametry ===== | ===== Podstawowe parametry ===== | ||

* Układ CPLD XC2C256 (256 makrokomórek) z rodziny CoolRunner-II w obudowie VQFP100 | * Układ CPLD XC2C256 (256 makrokomórek) z rodziny CoolRunner-II w obudowie VQFP100 | ||

| Line 21: | Line 21: | ||

|- | |- | ||

| style="text-align: center;"|<b> ZL14PLD </b> | | style="text-align: center;"|<b> ZL14PLD </b> | ||

| style="text-align: | | style="text-align: left;"| | ||

Zmontowany i uruchomiony moduł z układem XC2C256 | * Zmontowany i uruchomiony moduł z układem XC2C256 | ||

|} | |} | ||

</center> | </center> | ||

| Line 28: | Line 28: | ||

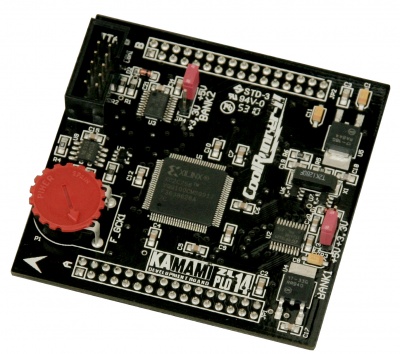

===== Schemat elektryczny ===== | ===== Schemat elektryczny ===== | ||

<center> | <center> | ||

[[File:zl14pld_sch.png|none| | [[File:zl14pld_sch.png|none|800px|thumb|center]] | ||

</center> | </center> | ||

| Line 51: | Line 51: | ||

===== Bufory dostosowujące do sygnałów o napięciu 5 V ===== | ===== Bufory dostosowujące do sygnałów o napięciu 5 V ===== | ||

Moduł wyposażony jest w dwa 8-liniowe bufory ST2378, które umożliwiają doprowadzenie do układu | Moduł wyposażony jest w dwa 8-liniowe bufory ST2378, które umożliwiają doprowadzenie do układu programowalnego 16 linii z sygnałami o napięciu 5 V lub 3,3 V. Konfiguracja buforów zależna jest od ustawienia zworek BANK1 (JP3) i BANK2 (JP4), opis konfiguracji przedstawiono w tabelce poniżej. | ||

<center> | <center> | ||

{| class="wikitable" style="width: 1000px;" | {| class="wikitable" style="width: 1000px;" | ||

Latest revision as of 10:15, 2 November 2024

Opis

Moduły dipPLD opracowano z myślą o ułatwieniu powszechnego stosowania układów CPLD przez konstruktorów, którzy nie mogą lub nie chcą inwestować w zautomatyzowany montaż elementów o relatywnie „gęstym” rastrze rozmieszczenia wyprowadzeń (0,5 mm).

Podstawowe parametry

- Układ CPLD XC2C256 (256 makrokomórek) z rodziny CoolRunner-II w obudowie VQFP100

- 16 linii z buforami dostosowującymi do sygnałów o napięciu 5 V

- Wbudowany regulowany generator sygnału taktującego oraz rezonator kwarcowy 32,768 kHz

- Moduł przystosowany do współpracy z płytą bazową ZL15PLD

Wyposażenie standardowe

| Kod | Opis |

|---|---|

| ZL14PLD |

|

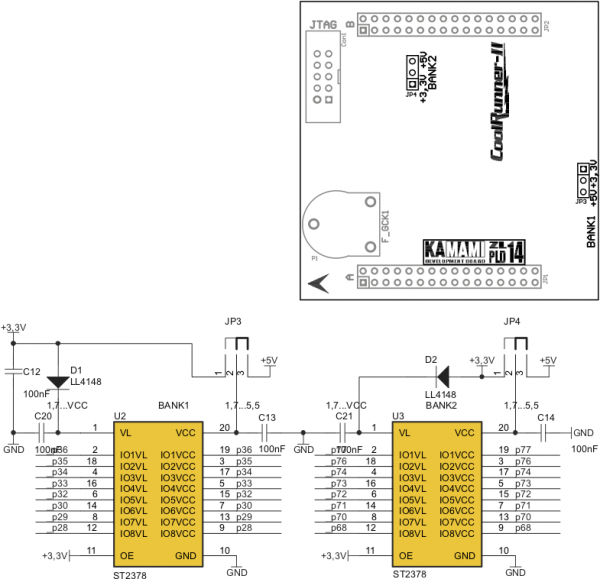

Schemat elektryczny

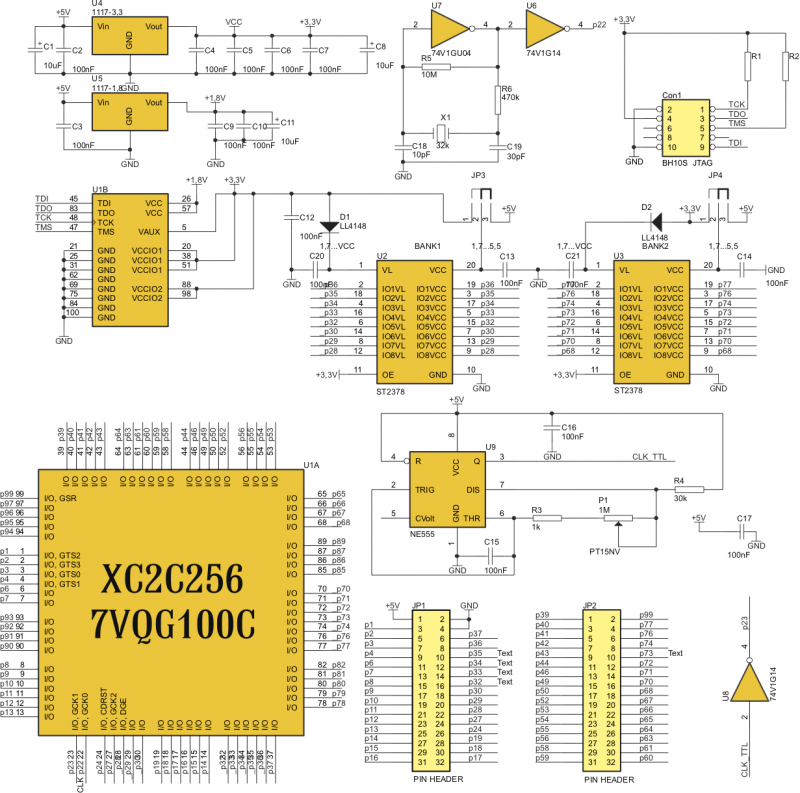

Rozmieszczenie najważniejszych elementów modułu

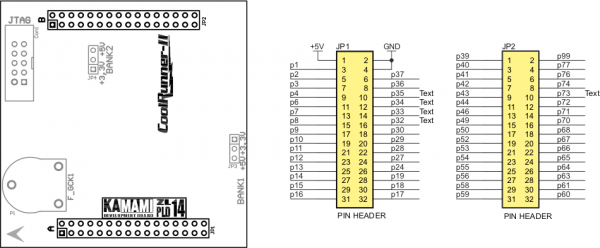

Wyprowadzenia modułu

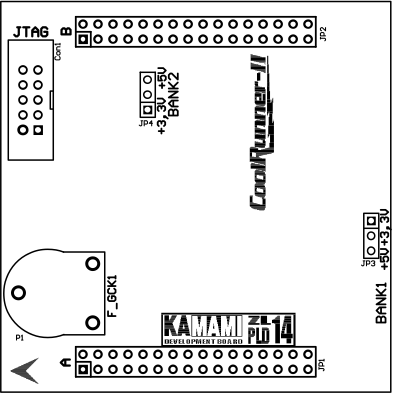

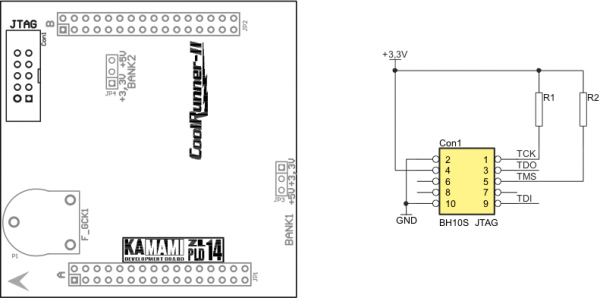

Złącze JTAG

Moduł wyposażono w 10-stykowe złącze IDC, do którego można dołączyć programator/konfigurator ISP (np. ZL11PRG lub ZL4PRG). Umieszczenie tego gniazda na płytce i rozmieszczenie sygnałów pokazano na rysunku poniżej.

Bufory dostosowujące do sygnałów o napięciu 5 V

Moduł wyposażony jest w dwa 8-liniowe bufory ST2378, które umożliwiają doprowadzenie do układu programowalnego 16 linii z sygnałami o napięciu 5 V lub 3,3 V. Konfiguracja buforów zależna jest od ustawienia zworek BANK1 (JP3) i BANK2 (JP4), opis konfiguracji przedstawiono w tabelce poniżej.

| Poziom sygnału | Linie I/O | Konfiguracja zworek |

|---|---|---|

| 3,3 V | p28, p29, p30, p32, p33, p34, p35, p36 | BANK1 w pozycji 3,3 V (1-2) |

| 5 V | p28, p29, p30, p32, p33, p34, p35, p36 | BANK1 w pozycji 5 V (2-3) |

| 3,3 V | p68, p70, p71, p72, p73, p74, p76, p77 | BANK2 w pozycji 3,3 V (1-2) |

| 5 V | p68, p70, p71, p72, p73, p74, p76, p77 | BANK2 w pozycji 5 V (2-3) |

Źródła sygnału taktującego

Moduł ZL14PLD jest wyposażony w dwa źródła sygnału taktującego: rezonator kwarcowy 32,768 kHz (X1) oraz regulowany generator oparty na timerze 555, którego częstotliwość regulowana jest za pomocą potencjometru F_GCK1 (P1).