JTAG Isolator (PL)

From Kamamilabs.com - Wiki

__jzXpdf__

Opis

JTAG Isolator jest galwanicznym separatorem interfejsu JTAG, zapobiegającym uszkodzeniom sprzętu wywołanym różnicami potencjałów odniesienia urządzeń łączonych ze sobą (np. komputera i płytki ewaluacyjnej) za pomocą interfejsu JTAG.

Podstawowe parametry

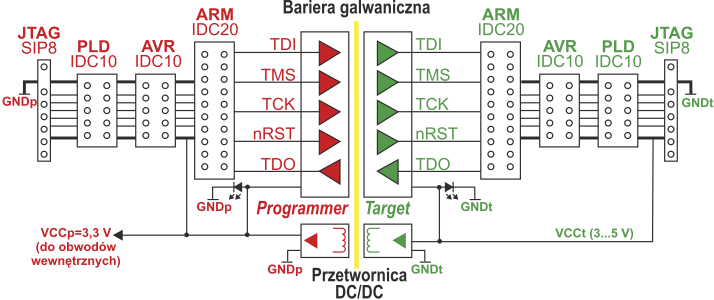

- Separacja galwaniczna 5-liniowego interfejsu JTAG

- Maksymalna częstotliwość taktowania TCK: 110 MHz(*)

- Zasilany z urządzenia docelowego (3...5 V)

- Zgodność ze wszystkimi interfejsami JTAG zasilanymi napięciem 3...5 V

- Poziomy logiczne po stronie Programmer: TTL/TTL-LV

- Poziomy logiczne po stronie Target: TTL-LV

- Maksymalny pobór prądu: 50 mA

- Napięcie izolacji: 750 VAC/1 kVDC

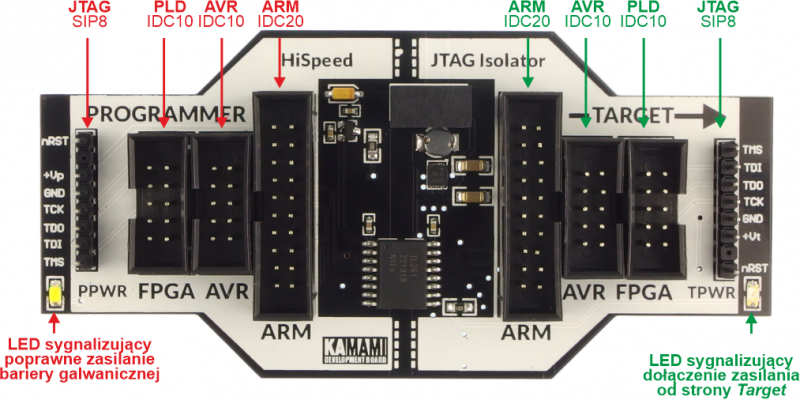

- Optyczna sygnalizacja dołączenia zasilania

- Optyczna sygnalizacja zasilania bariery galwanicznej

- Wbudowane złącza:

- IDC10 – JTAG dla PLD (FPGA i CPLD) – zgodne z programatorem Altera ByteBlaster, IDC10 ** JTAG dla mikrokontrolerów AVR,

- IDC20 – JTAG dla mikrokontrolerów i mikroprocesorów ARM,

- SIP8 – JTAG dla PLD (FPGA i CPLD) – zgodne z programatorem Digilent JTAG HS1.

- Prąd pobierany z linii +Vp przez programator: maks. 10 mA

(*) Zależy od długości przewodów połączeniowych

| Nie wolno łączyć ze sobą ani jednocześnie dotykać wyprowadzeń separatora po stronach Target i Programmer – mogą one znajdować się na różnych potencjałach, co może grozić porażeniem operatora lub uszkodzeniem sprzętu. |

Wyposażenie standardowe

| Kod | Opis |

|---|---|

| JTAG Isolator |

|

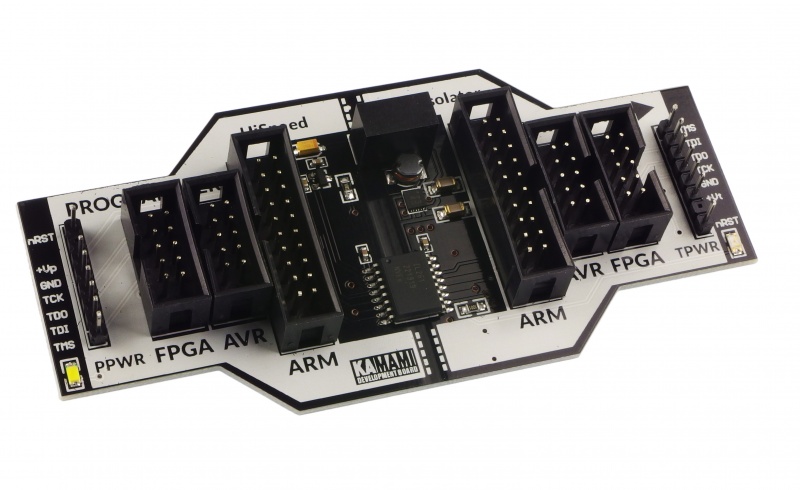

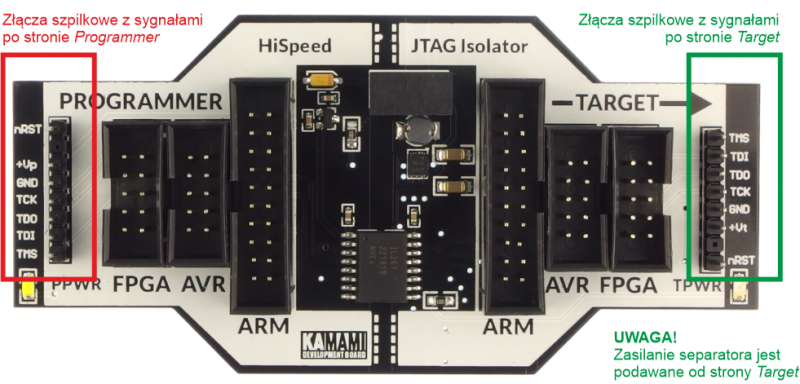

Rozmieszczenie najważniejszych elementów

Schemat blokowy

Zasilanie separatora

Obydwie strony elektryczne (Target i Programmer) separatora są zasilane od strony Target. Energię elektryczną dla obwodów strony Programmer dostarcza wbudowana w urządzenie, galwanicznie separowana przetwornica DC/DC. Z tego względu konieczne jest zapewnienie dodatkowego prądu zasilającego separator, którego wartość jest zależna od napięcia zasilającego (jak w tabeli poniżej). Programator dołączony po stronie Programmer powinien być zasilany z osobnego źródła, dopuszczalne jest zasilanie z linii +Vp separatora wyłącznie buforów I/O. Maksymalna obciążalność linii +Vp wynosi 10 mA @3,3 V.

Pobór prądu przez separator z zasilacza po stronie Target

| Napięcie +Vt [V] | Pobór prądu od strony +Vt [mA |

|---|---|

| 3 | <50 |

| 3,3 | <45 |

| 4 | <30 |

| 5 | <35 |

Dopuszczalne poziomy logiczne

Separator od strony Target może być zasilany napięciem o wartości od Vt = 3 do Vt = 5 V. Poziomy akceptowanych napięć na liniach wejściowych i wyjściowych wynoszą od 0 V do Vt, przy czym zakres napięć dla logicznego „0” wynosi od 0 do 0,8 V, a dla „1” wynosi od 2,4...Vt. Po stronie Programmer zalecane jest dołączanie interfejsów programujących z buforami I/O zasilanymi napięciem o wartości Vp = 3,3 V. Zakres napięć dla logicznego „0” wynosi 0...0,8 V, a dla „1” wynosi od 2,4...Vp. Przekroczenie po stronie Programmer na liniach I/O wartości napięcia Vp może spowodować uszkodzenie separatora.

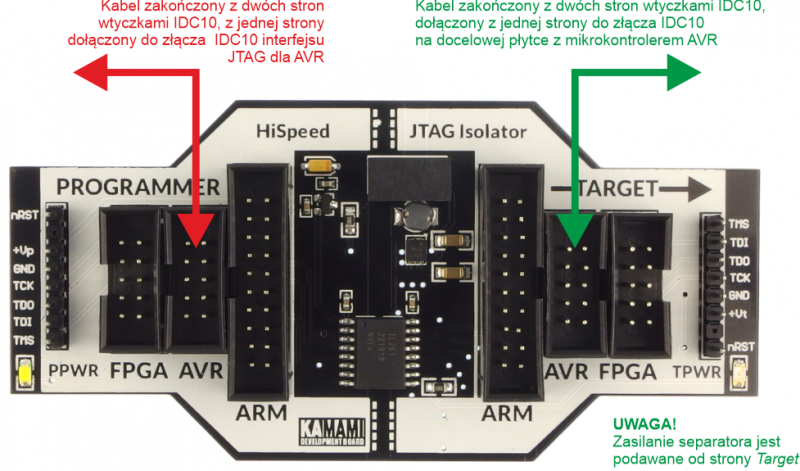

Połączenia dla AVR

Separator od strony Target może być zasilany napięciem o wartości od Vt = 3 do Vt = 5 V. Poziomy akceptowanych napięć na liniach wejściowych i wyjściowych wynoszą od 0 V do Vt, przy czym zakres napięć dla logicznego „0” wynosi od 0 do 0,8 V, a dla „1” wynosi od 2,4...Vt. Po stronie Programmer zalecane jest dołączanie interfejsów programujących z buforami I/O zasilanymi napięciem o wartości Vp = 3,3 V. Zakres napięć dla logicznego „0” wynosi od 0...0,8 V, a dla „1” wynosi od 2,4...Vp. Przekroczenie po stronie Programmer na liniach I/O wartości napięcia Vp może spowodować uszkodzenie separatora.

| Maksymalna częstotliwość sygnału TCK może wynosić 110 MHz. Jest ona silnie zależna od długości kabli i ścieżek połączeniowych (im dłuższe, tym fTCKmax jest niższa) i charakteru obciążenia poszczególnych linii I/O po stronie Target. |

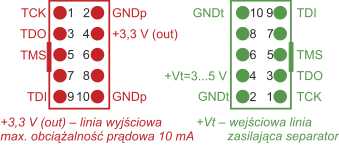

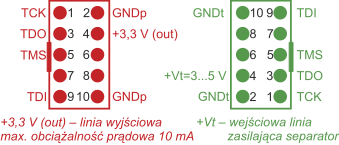

Przypisanie sygnałów po do złącza AVR stronie Programmer (czerwone) i Target (zielone).

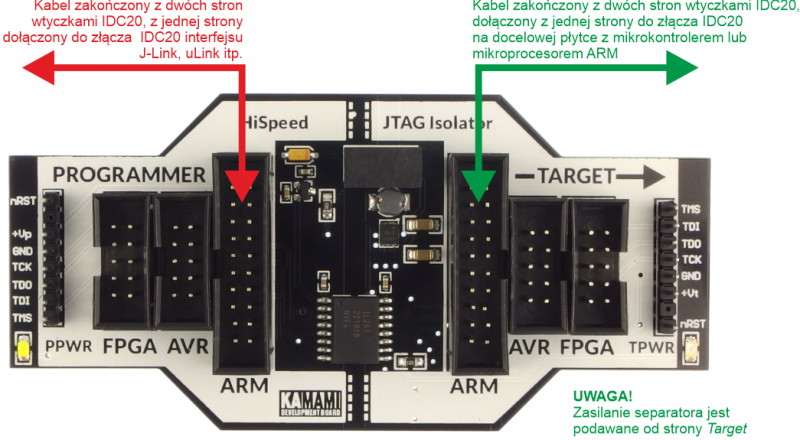

Połączenia dla ARM

Sposób zastosowania separatora JTAG Isolator do programowania/debugowania systemu z mikrokontrolerem ARM

| Maksymalna częstotliwość sygnału TCK może wynosić 110 MHz. Jest ona silnie zależna od długości kabli i ścieżek połączeniowych (im dłuższe, tym fTCKmax jest niższa) i charakteru obciążenia poszczególnych linii I/O po stronie Target. |

Przypisanie sygnałów po do złącza ARM stronie Programmer (czerwone) i Target (zielone)

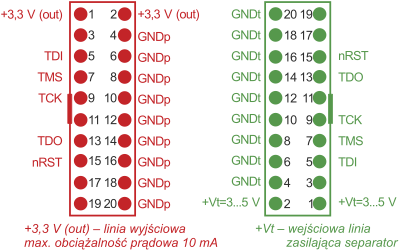

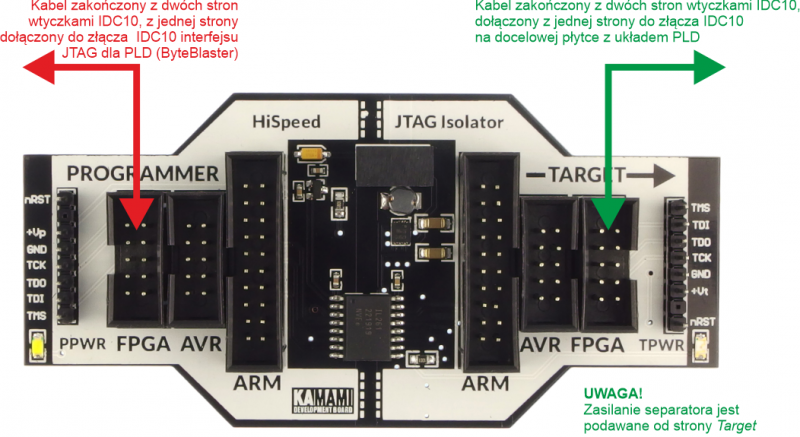

Połączenia dla PLD (CPLD/FPGA)

| Maksymalna częstotliwość sygnału TCK może wynosić 110 MHz. Jest ona silnie zależna od długości kabli i ścieżek połączeniowych (im dłuższe, tym fTCKmax jest niższa) i charakteru obciążenia poszczególnych linii I/O po stronie Target. |

Przypisanie sygnałów po do złącza PLD (zgodne z ByteBlaster) stronie Programmer (czerwone) i Target (zielone)

Połączenia dla dowolnego interfejsu JTAG

Separator wyposażono w złącze szpilkowe SIP8 ze stykami w rastrze 2,54 mm, do których można dołączyć dowolne interfejsy JTAG lub inne, wymagające separacji galwanicznej.

Rozmieszczenie sygnałów na złączach szpilkowych umożliwia bezpośrednie zainstalowanie na nich programatora-konfiguratora układów programowalnych Digilent JTAG HS1 (fotografia poniżej).